Slik optimaliserer du designet ditt og unngår vanlige signal- og strømintegritetsproblemer

Utviklingen innen elektronikk har akselerert i flere tiår, og alt tyder på at tempoet bare vil øke i fremtiden. Etter hvert som behovet for raskere, mer energieffektive og mindre enheter fortsetter å vokse, blir utfordringer knyttet til signal- og strømintegritet stadig vanligere. Som elektronikkingeniør eller -designer er det viktig å kjenne til fallgruvene – og, enda viktigere, vite hvordan du kan løse dem.

Fallgruvene inkluderer:

- Karakteristisk impedans

- IR Drop

- Krysstale (Crosstalk/Xtalk)

- Returveier

- Loop-induktans for avkoblingskondensatorer (Decoupling Capacitors)

Kunnskapen om disse problemene og teoriene bak dem er godt kjent i markedet. Utfordringen ligger i hvordan de enkelt kan identifiseres og løses tidlig i designprosessen, for å unngå forsinkelser i tidsplanen og stressende feilsøkingsøkter.

Løsningen på disse utfordringene er å bruke et verktøy som Sigrity.

Impedans og refleksjoner

Mange grensesnitt stiller krav til kontroll av karakteristisk impedans for sporene. Hvis dette ikke håndteres korrekt – for eksempel på grunn av feil impedans eller dårlig sporutforming – kan det føre til redusert signalintegritet. Resultatet kan bli et lukket øyediagram på grunn av over- og undershoot. Impedans for spor bestemmes i hovedsak av stackup-geometri og materialspesifikasjoner. Viktige parametere er:

- Materialegenskaper (dielektrisk konstant)

- Sporgeometri (bredde og tykkelse)

- Dielektrisk tykkelse (avstand mellom spor og returplan)

- Transmisjonslinjetopologi (f.eks. microstrip, stripline eller nedgravd microstrip med loddemaske)

Vanlige årsaker til feil relatert til karakteristisk impedans:

- Endringer i stackup etter påbegynt routing: Hvis designet er basert på en spesifikk sporvidde for ønsket impedans, og produsenten endrer stackup eller lagtykkelser etter routing, kan dette føre til avvik.

- Feilaktige impedansberegninger: Produsentens beregninger kan være unøyaktige. Gå alltid gjennom dokumentasjonen for stackup fra produsenten og dobbeltsjekk impedanstabellen.

- Feilberegning av avstand i differensialpar: Forveksling av senter-til-senter-avstand med kant-til-kant-avstand kan gi feil i impedanskontrollen.

- Utelatelse av metalltykkelse eller loddemaske: Hvis beregningene ikke tar hensyn til sporens tykkelse eller tilstedeværelsen av loddemaske, kan dette føre til avvik i impedansen.

Slik optimaliserer du designet ditt:

- Samarbeid tett med produsenten, og bruk alltid en field solver for å beregne sporvidder.

- Sørg for å route med korrekt sporvidde og avstand ved hjelp av definerte regler.

- Vær oppmerksom på hull og avgrensninger i referanseplanet, og sørg for at spor alltid rutes over en kontinuerlig returvei.

- Juster stackupen hvis det er vanskelig å oppnå passende sporvidde basert på lagtykkelsene. Tynne lag kan kreve smalere spor for å oppnå ønsket impedans.

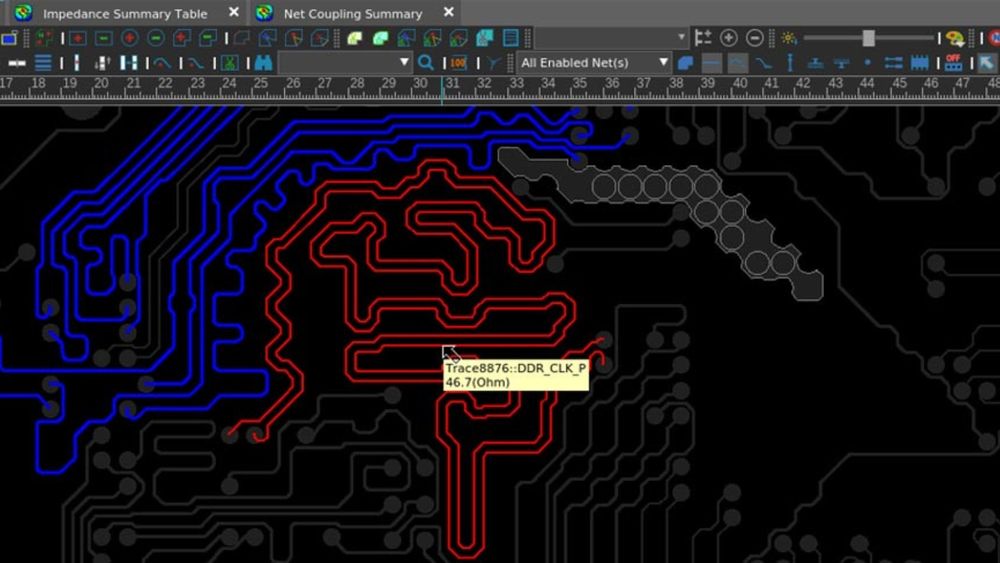

Bruk grafisk fargekoding av sporimpedanser i Cadence Sigrity Starter Kit for raskt å identifisere områder der impedansen avviker fra det forventede.

IR Drop og stabilitet

Dette refererer til spenningsfallet langs en leder når en likestrøm (DC) går gjennom den. Tapsfenomenet skyldes lederens motstand, som forårsaker en spenningsforskjell mellom strømforsyningen og komponentene.

Aktive komponenter kan bli ustabile fordi de opplever spenninger lavere enn minimumsgrensene for forsyningsspenning. Dersom spenningsfallet er større enn forventet, reduseres også marginen for eventuell AC-ripple.

Vanlige årsaker til spenningsfall:

- For tynne kobberlag i stackupen, for smale ledere eller begrensede kobberområder i forsyningsnettet.

- For få eller feilplasserte vias.

- Høyere strømmer kan forårsake større spenningsfall og øke dette ytterligere ettersom kobberets motstand stiger med temperaturen.

- Seriekomponenter som spoler, ferritter (ferrite beads) og sense-motstander kan også bidra til spenningsfall.

- Feil plassering av sense-motstand til feedback-løkken kan gjøre at reguleringen ikke kompenserer for spenningsfall i kretsen.

Slik kan du optimalisere designet ditt:

- Om mulig, bruk tykkere kobber på forsyningsplaner, men vær oppmerksom på hvordan dette påvirker minimumsstørrelser for ledningsbredde, avstander, ringarealer osv.

- Utnytt PCB-arealet og bruk så brede planer/ledere som mulig. Økt tverrsnittsareal reduserer motstanden.

- Minimer avstanden mellom strømforsyning (VRM) og belastning (SINK) for å redusere motstanden.

- Bevar mest mulig kobber ved å minimere størrelsen på via-anti-pads. Ta hensyn til produsentens grenser for boring og kobberavstand.

- Dobbeltsjekk at det er nok vias ved hver overgang for å redusere motstanden. Alternativt kan ekstra plating i vias bidra til å senke resistansen.

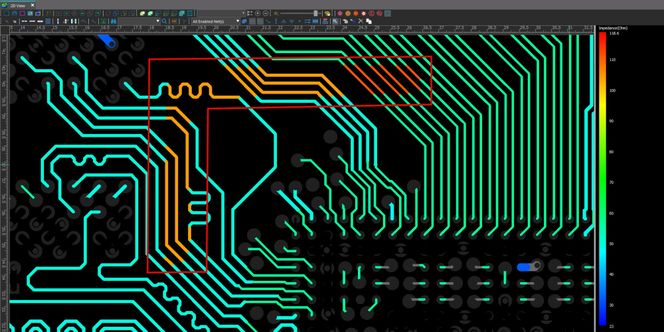

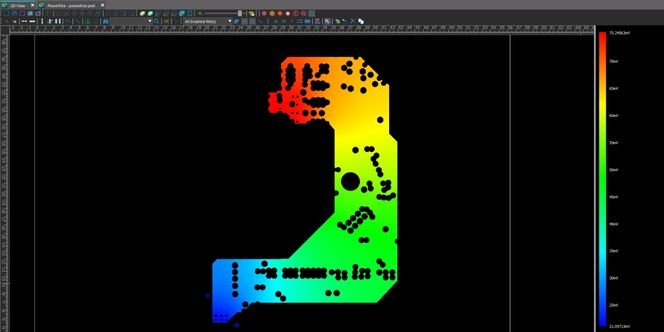

Cadence Sigrity Starter Kit tilbyr simulering med visuell fargekoding av layoutet, slik at du enkelt kan identifisere spenningsfallet, lokalisere hvor det oppstår, og i hvilke strukturer. I simuleringen kan du også teste alternative materialer i stackupen, noe som er langt enklere enn å lage nye PCB-spinn.

Kobling og krysstale

Krysstale defineres som støy på et signal (offer) forårsaket av et annet forstyrrende signal (aggressor) på grunn av elektrisk og magnetisk kobling mellom lederne. I verste fall kan dette føre til for høy eller for lav spenning for mottakeren. Fra et designperspektiv er målet å minimere koblingen mellom ledere og dermed redusere krysstalen.

Vanlige årsaker til krysstale:

- For liten avstand mellom ledere, som gir sterkere kobling.

- For stor avstand til referanselag (tykke laminater), som øker koblingen mellom lederne i stedet for koblingen til referanselaget.

- Rask stige- og falltid på signaler, da indusert spenning avhenger av endringstiden.

- Dårlig returvei, som også øker krysstale.

- Flere signallag direkte inntil hverandre, noe som kan gi krysstale mellom signaler som er routet oppå hverandre.

Slik kan du optimalisere designet ditt:

- Definer regler for avstand mellom ledere så tidlig som mulig i designprosessen. Bruk gjerne krysstalesimulering for å fastsette passende regler.

- Bruk så tynne laminater som mulig mellom signal- og referanselag, men husk at tynnere laminater påvirker lederbredder for impedansstyrte ledere.

- Hvis du har to signallag i stackupen som ligger ved siden av hverandre, kan ortogonal routing minimere krysstale.

- Konfigurer aktive kretser til å bruke langsommere stige- og falltider hvis mulig, da dette også reduserer krysstale.

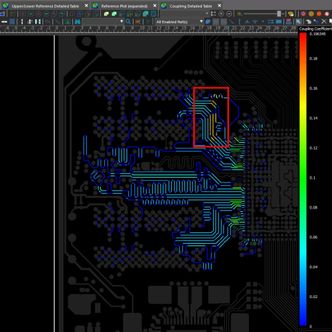

Cadence Sigrity Starter Kit tilbyr analyser som beregner koblingen mellom ledere. Resultatene kan vises som en fargekoding i layoutet, slik at du enkelt kan identifisere områder med høy kobling og adressere det tidlig i designet.

Returveier

Kretsteorien fastslår at strøm bare kan flyte i en lukket krets. I moderne design er det enkelt å følge signalet fra sender til mottaker, men for at dette skal fungere, må det også flyte en strøm tilbake fra mottakeren til senderen.

Ideelt sett ønsker man som designer å lage en "usynlig" returvei gjennom planlag og vias tilbake til senderen som er like effektiv som signalveien. Men siden denne returveien er usynlig, kan det være vanskelig å sjekke og kontrollere. Mangelfull returvei kan ofte avsløres av refleksjoner og økt krysstale.

Vanlige årsaker til problemer med returveier:

- En av de vanligste feilene er å route en leder over diskontinuiteter i referanseplanet. Dette skjer typisk hvis du har flere strømforsyningsbaner på samme lag i layoutet.

- En annen vanlig feil er manglende returstrømsvias ved lagbytte. Når et signal bytter fra ett lag til et annet, bør det ideelt sett plasseres en retur-via i nærheten, slik at returstrømmen kan flyte gjennom den.

- Overlappende anti-pads fra vias og komponentbein kan også forårsake problemer i returveien for signalene.

Slik kan du optimalisere designet ditt:

- Juster planlag og ledere for å sikre intakte referanseplaner.

- Legg til vias for returstrøm ved lagbytter for signaler. I spesifikke situasjoner kan det være nyttig å simulere seg frem til den ideelle strukturen for signal- og returstrømsvias.

- Med Cadence Sigrity Starter Kit kan du enkelt visualisere og finne forbindelser som trenger oppmerksomhet gjennom rapporter. Slik kan du bruke tiden din der det trengs mest og unngå å overse kritiske problemer.

Avkoblingskondensatorer

Langt de fleste elektriske kretser trenger avkoblingskondensatorer for å minimere AC ripple på strømforsyningene og for å redusere EMI-problemer.

Selv om det finnes flere ulike typer avkoblingskondensatorer, er de alle begrenset av egen induktans i høyere frekvensområder. Induktansen for en avkobling påvirkes av flere faktorer som fysisk størrelse, intern oppbygning, tilkobling og lagstruktur.

Vanlige årsaker til problemer med strømforsyningsnett og avkoblinger:

- Monteringsinduktans på avkoblingskondensatorer begrenser funksjonaliteten deres, og du må ofte bruke flere kondensatorer i parallell for å dekke ulike frekvensområder.

- Lange, tynne ledninger som forbinder avkoblingskondensatorer til strømforsyningsplaner, øker induktansen.

- Hvis en avkoblingskondensator skal kobles til planer på motsatt side av plasseringen, økes også induktansen.

- Fysisk store avkoblingskondensatorer har høyere induktans enn små kondensatorer.

Slik kan du optimalisere designet ditt:

- Bruk Excel eller andre nettverktøy til å bestemme hvor mange avkoblinger du trenger for å ha et stabilt system.

- Design stackup-en slik at du får så lav induktans som mulig når du monterer avkoblingskondensatorene.

- Plasser og koble avkoblingskondensatorene med korte og brede forbindelser til strømforsyningsplanene for å minimere induktansen.

Med Cadence Sigrity Starter Kit kan du ekstrahere loop-induktans for alle avkoblinger og bruke fargekoding på layoutet for å identifisere avkoblinger med suboptimal tilkobling.

Problemer med SI/PI er enklest å løse før og under layout-fasen i designprosessen. Med grundig planlegging kan du minimere feil tidlig i prosessen, men tidspress kan ofte hindre deg i å oppnå en ideell arbeidsflyt.

Cadence Sigrity Starter Kit lar deg holde oversikt over utfordringer innen signal- og strømintegritet gjennom hele layoutfasen. Ved hjelp av analyser og intuitiv fargekoding blir prosessen mer oversiktlig, noe som sparer tid, energi og ressurser.

Hvis du vil vite mer, kan du delta på Nordcad sitt live-webinar onsdag 5. februar, hvor vår Senior Application Engineer, Søren Christiansen, går gjennom Sigrity Starter Kit. Webinaret holdes kl. 10.00 på dansk og kl. 14.00 på engelsk.